### Mode 0 Operation

Mode 0 operation causes the 82C55 to function either as a buffered input device or as a latched output device. These are the same as the basic input and output circuits discussed in the first section of this chapter.

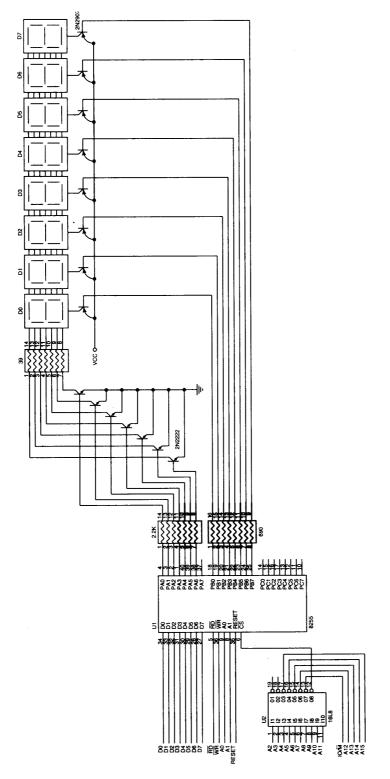

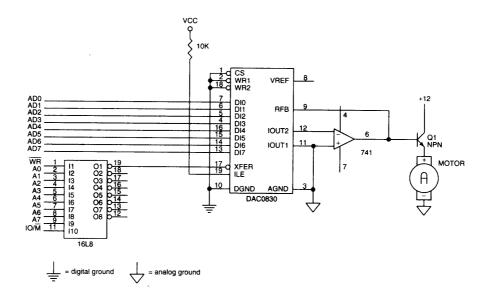

Figure 10–20 shows the 82C55 connected to a set of eight 7-segment LED displays. In this circuit, both ports A and B are programmed as (mode 0) simple latched output ports. Port A provides the segment data inputs to the display and port B provides a means of selecting one display position at a time for multiplexing the displays. The 82C55 is interfaced to an 8088 microprocessor through a PAL16L8 so that it functions at I/O port numbers 0700H–0703H. The program for the PAL16L8 is listed in Example 10–7. The PAL decodes the I/O address and develops the write strobe for the WR pin of the 82C55.

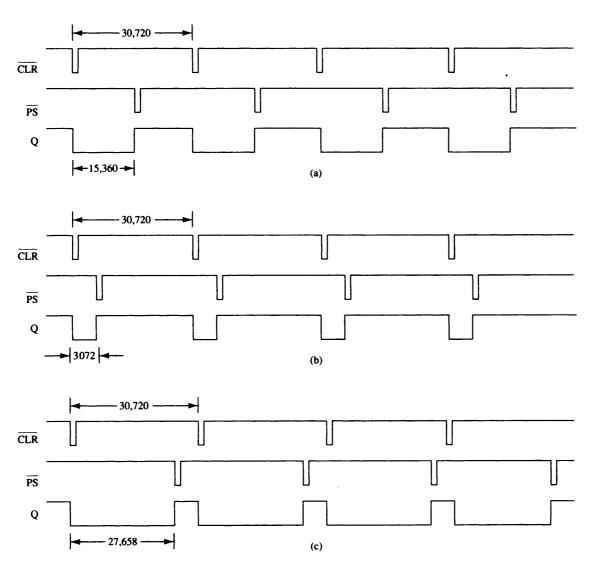

### **EXAMPLE 10-7**

```

CHIP DECODERD PAL16L8

;pins 1 2 3 4 5 6 7 8 9 10

A2 A3 A4 A5 A6 A7 A8 A9 A10 GND

;pins 11 12 13 14 15 16 17 18 19 20

A11 CS IOM A12 A13 A14 A15 NC NC VCC

EQUATIONS

/CS = /A15 * /A14 * /A13 * /A12 * /A11 *

A10 * A9 * A8 * /A6 * /A5 * /A4 * /A3 * /A2

* /IOM

```

The resistor values are chosen in Figure 10-20 so that the segment current is 80 mA. This current is required to produce an average current of 10 mA per segment as the displays are multiplexed. A 6-digit display uses a segment current of 60 mA, for an average of 10 mA per segment. In this type of display system, only one of the eight display positions is on at any given instant. The peak anode current in an 8digit display is 560 mA (seven segments  $\times$  80 mA), but the average anode current is 80 mA. In a 6-digit display, the peak current would be 420 mA (seven segments × 60 mA). Whenever displays are multiplexed, we increase the segment current from 10 mA (for a display that uses 10 mA per segment as the nominal current) to a value equal to the number of display positions times 10 mA. This means that a 4digit display uses 40 mA per segment, a 5-digit display uses 50 mA, and so on.

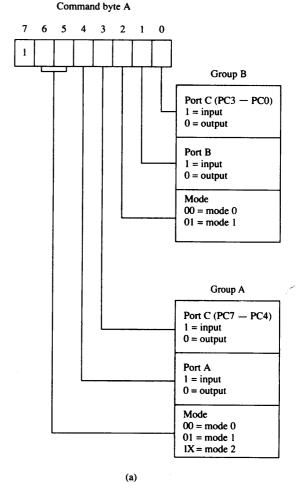

**FIGURE 10–19** The command byte of the command register in the 82C55. (a) Programs ports A, B, and C (b) Sets or resets the bit indicated in the select a bit field.

FIGURE 10-20 An 8-digit LED display interfaced to the 8088 microprocessor through an 82C55 PPI.

In this display, the segment load resistor passes 80 mA of current and has a voltage of approximately 3.0 V across it. The LED (1.65 V nominally) and a few tenths are dropped across the anode switch and the segment switch, hence a voltage of 3.0 V appears across the segment load resistor. The value of the resistor is  $^{3.0 \text{ V}}/80 \text{ mA}$  = 37.5 \*. The closest standard resistor value of 39 \* is used in Figure 10–20 for the segment load.

The resistor in series with the base of the segment switch assumes that the minimum gain of the transistor is 100. The base current is therefore  $^{80 \text{ mA}}/100 = 0.8 \text{ mA}$ . The voltage across the base resistor is approximately 3.0 V (the minimum logic 1 voltage level of the 82C55), minus the drop across the emitter-base junction (0.7 V), or 2.3 V. The value of the base resistor is then 2.3 V/0.8 mA = 2.875 K\*. The closest standard resistor value is 2.7 K\*, but a 2.2 K\* is chosen for this circuit.

The anode switch has a single resistor on its base. The current through the resistor is 560 mA/100 = 5.6 mA because the minimum gain of the transistor is 100. This exceeds the maximum current of 4.0 mA from the 82C55, but this is small enough so that it will work without problems. The maximum current assumes that you are using the port pin as a TTL input to another circuit. If the amount of current were over 8.0-10.0 mA, then appropriate circuitry (in the form of either a Darlington-pair or another transistor switch) would be required. Here, the voltage across the base resistor is 5.0 V, minus the drop across the emitter-base junction (0.7 V), minus the voltage at the port pin (0.4 V), for a logic 0 level. The value of the resistor is 3.9 V/5.6 mA = 696 W. The closest standard resistor value is 690 W, which is chosen for this example.

Before software to operate the display is examined, we must first program the 82C55. This is accomplished with the short sequence of instructions listed in Example 10–8. Here, port A and B are both programmed as outputs.

### **EXAMPLE 10-8**

```

;programming the 82C55 PIA

;

0000 B0 80 MOV AL,10000000B

0002 BA 0703 MOV DX,703H ;address command

0005 EE OUT DX,AL ;program 82C55

```

The procedure to multiplex the displays is listed in Example 10–9. For the display system to function correctly, we must call this procedure often. Notice that the procedure calls another procedure (DELAY) that causes a 1 ms time delay. The time delay is not illustrated in this example, but it is used to allow time for each display position to turn on. It is recommended by the manufacturers of LED displays that the display flash be between 100 Hz and 1500 Hz. Using a 1 ms time delay, we light each digit for 1 ms for a total display flash rate of 1000 Hz/8 display, or a flash rate of 125 Hz.

### **EXAMPLE 10-9**

```

; Procedure that multiplexes the 8-digit LED display.

; This procedure must be called from a program at

; whenever possible to display 7-segment

; coded data from memory.

0006

DISP

PROC NEAR USES AX BX DX SI

000A 9C

PUSHE

; save flag register

;setup registers for display

000B BB 0008

MOV

BX,8

;load count

000E B4 7F

MOV

AH,7FH

;load selection pattern

0010 BE 00FF R

SI,OFFSET MEM-1 ;address data

MOV

0013 BA 0701

MOV

DX,701H

;address Port B

;display 8 digits

```

### 304 CHAPTER 10 BASIC I/O INTERFACE

| 0016 |    |      |   | DISP1 | :    |            |                       |

|------|----|------|---|-------|------|------------|-----------------------|

| 0016 | 8A | C4   |   |       | MOV  | AL,AH      | ;select a digit       |

| 0018 | EE |      |   |       | OUT  | DX,AL      |                       |

| 0019 | 4A |      |   |       | DEC  | DX         | ;address Port A       |

| 001A | 8A | 00   |   |       | MOV  | AL,[BX+SI] | get 7-segment data;   |

| 001C | EE |      |   |       | OUT  | DX,AL      |                       |

| 001D | E8 | 029A | R |       | CALL | DELAY      | ;wait one millisecond |

| 0020 | D0 | CC   |   |       | ROR  | AH,1       | ;address next digit   |

| 0022 | 42 |      |   |       | INC  | DX         | ;address Port B       |

| 0023 | 4B |      |   |       | DEC  | BX         | ;adjust count         |

| 0024 | 75 | F0   |   |       | JNZ  | DISP1      | repeat 8 times;       |

|      |    |      |   |       |      |            |                       |

| 0026 | 5E |      |   |       | POPF |            | restore registers;    |

|      |    |      |   |       | RET  |            |                       |

|      |    |      |   |       |      |            |                       |

| 0020 |    |      |   | DISP  | ENDP |            |                       |

|      |    |      |   |       |      |            |                       |

The display procedure (DISP) addresses an area of memory where the data, in 7-segment code, is stored for the eight display digits called MEM. The AH register is loaded with a code (7FH) that initially addresses the most-significant display position. Once this position is selected, the contents of memory location MEM +7 is addressed and sent to the most-significant digit. The selection code is then adjusted to select the next display digit, as is the address. This process repeats eight times to display the contents of location MEM through MEM +7 on the eight display digits.

An LCD Display Interfaced to the 82C55. LCDs (liquid crystal displays) are quickly replacing LED displays in many applications. The only disadvantage of the LCD display is that it is difficult to see in low-light situations in which the LED is still in limited use.

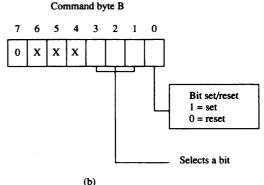

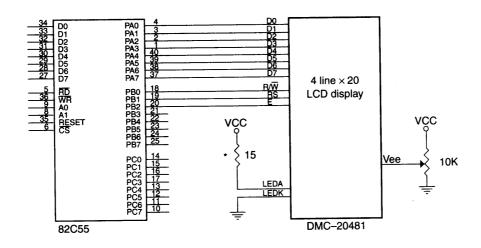

Figure 10–21 illustrates the connection of the Optrex DMC-20481 LCD display to an 82C55. The DMC-20481 is a 4-line by 20-characters-per-line display that accepts ASCII code as input data. It also accepts commands that initialize it and control its application. As you can see in Figure 10–21, the LCD display has few connections. The data connections, which are attached to the 82C55 Port A, are used to input display data and to read information from the display.

\*Note: Current max is 480 mA, nominal 260 mA

There are four control pins on the display. The VEE connection is used to adjust the contrast of the LED display and is normally connected to a 10 K\* potentiometer, as illustrated. The RS (register select) input selects data (RS = 1) or instructions (RS = 0). The E (enable) input must be a logic 1 for the DMC-20481 to read or write information. Finally, the R/W pin selects a read or a write operation. Normally, the RS pin is placed at a 1 or 0, the R/W pin is set or cleared, data are placed on the data input pins, and then the E pin is pulsed to access the DMC-20481. This display also has two inputs for back-lighting LED diodes, which are not shown in the illustration.

In order to program the DMC-20481 we must first initialize it. This applies to any display that uses the HD44780 (Hitachi) display driver integrated circuit. The entire line of small display panels from Optrex is programmed in the same manner. Initialization is accomplished via the following steps:

- 1. Wait at least 15 ms after Vcc rises to 5.0 V.

- 2. Output the function set command (30H), and wait at least 4.1 ms.

- 3. Output the function set command (30H) a second time, and wait at least 100 ③.

- 4. Output the function set command (30H) a third time, and wait at least 40 ③.

- 5. Output the function set command (38H) a fourth time, and wait at least 40 3.

- 6. Output a 08H to disable the display, and wait at least 40 🔾.

- 7. Output a 01H to home the cursor and clear the display, and wait at least 1.64 ms.

- 8. Output the enable display cursor off (0CH), and wait at least 40 ③.

- 9. Output a 06H to select auto-increment, shift the cursor, and wait at least 40 ③.

The software to accomplish the initialization of the LCD display is listed in Example 10–10. It is long, but the display controller requires the long initialization dialog. Note that the software for the three time delays is not included in the listing. If you are interfacing to a PC, you can use the clock tick discussed in Chapter 7 for the time delay. One clock tick can be used for all timing in this software, even though the LCD display will function faster than your eye at 1/18 seconds. If you are developing the interface for another application, then you must write three separate time delays, which must provide the delay times indicated in the initialization dialog.

### **EXAMPLE 10-10**

|                              |                |                  | ;proc | edure                       | to initialize                          | e the LCD display                                                        |

|------------------------------|----------------|------------------|-------|-----------------------------|----------------------------------------|--------------------------------------------------------------------------|

| 0010                         |                |                  | INIT  | PROC                        | NEAR                                   |                                                                          |

| 0010<br>0013<br>0015         | в0             |                  |       | VOM<br>VOM<br>TUO           | DX,CMD8255<br>AL,80H<br>DX,AL          | ;address 8255 command register ;all ports are output ports               |

| 0016<br>0018<br>001B         | BA             |                  |       | VOM<br>VOM<br>TUO           | AL,0<br>DX,PORTB<br>DX,AL              | ;clear Port B                                                            |

| 001C<br>001F<br>0021<br>0024 | B0<br>E8       | 30<br>002A       |       | CALL<br>MOV<br>CALL<br>CALL | DELAY15<br>AL,30H<br>OUTCMD<br>DELAY41 | <pre>;wait 15 ms ;first function set command ;send it ;wait 4.1 ms</pre> |

| 0027<br>0029<br>002C<br>002E | B0<br>E8<br>B0 | 30<br>0022<br>30 |       | MOV<br>CALL<br>MOV<br>CALL  | AL, 30H<br>OUTCMD<br>AL, 30H<br>OUTCMD | ; second function set command ; third function set command               |

| 0031<br>0033<br>0036         | B0<br>E8<br>E8 | 38<br>0018       |       | MOV<br>CALL<br>CALL         | AL,38H<br>OUTCMD<br>DELAY100           | ; fourth function set command                                            |

| 0039 1<br>003B 1<br>003E 1   | E8<br>B0       | 01               |       | MOV<br>CALL<br>MOV<br>CALL  | AL,08H<br>OUTCMD<br>AL,01H<br>OUTCMD   | display off; clear display                                               |

| 0043                         |                |                  |       | MOV                         | AL, OCH                                | ;display on, cursor off                                                  |

### 306 CHAPTER 10 BASIC I/O INTERFACE

```

0045 E8 0006

CALL OUTCMD

0048 B0 06

MOV

AL,06H

;auto-increment, shift cursor

004A E8 0001

OUTCMD

CALL

004D C3

RET

004E

INIT

ENDP

;procedure to output a command

004E

OUTCMD

PROC NEAR

004E 50

PUSH AX

; save command

004F BA 0303

MOV

DX, CMD8255

;select 8255 command resgiter

0052 B0 80

MOV

AL,80H

;all ports are outputs

0054 EE

OUT

DX,AL

DX, PORTA

0055 BA 0300

MOV

0058 58

POP

AX

0059 EE

OUT

DX, AL

; command to port A

;address Port B

005A 42

INC

DX

005B B0 04

MOV

AL,4

;put 1 on E, 0 on R/W# and 0 on S

005D EE

OUT

DX, AL

005E 90

NOP

;extra time so E = 1 longer

005F 90

NOP

0060 B0 00

MOV

AL.O

;clear E

0062 EE

OUT

DX, AL

;wait 100 us

0063 E8 0029

CALL

DELAY100

0066 C3

RET

0067

OUTCMD

ENDP

```

The NOP instructions are added in the OUTCMD procedure to ensure that the E bit remains a logic 1 long enough to activate the LCD display. This process should work in most systems at most clock frequencies, but additional NOP instructions may be needed to lengthen this time in some cases.

Before programming data to the display, the commands used in the initialization dialog must be explained. See Table 10–3 for a complete listing of the commands or instructions for the LCD display. Compare the commands sent to the LCD display in the initialization program to Table 10–3.

Once the LCD display is initialized, a few procedures are needed to display information and control the display. After initialization, time delays are no longer needed when sending data or many commands to the display. The clear display command still needs a time delay because the busy flag is not used with that command. Instead of a time delay, the busy flag is tested to see whether the display has completed an operation. A procedure to test the busy flag appears in Example 10–11. The BUSY procedure tests the LCD display and only returns when the display has completed a prior instruction.

### **EXAMPLE 10-11**

```

;procedure to test busy and return if not busy

:0010

BUSY PROC

NEAR

.REPEAT

0010 BA 0303

DX, CMD8255

;select 8255 command register

MOV

\Box

AL,90H

0013 B0 90

MOV

;port A input

0015 EE

OUT

DX, AL

0016 BA 0301

DX, PORTB

MOV

;select port B

:R/W# = 1

0019 B0 01

MOV

AL,1

OUT

001B EE

DX, AL

001C B0 05

MOV

;R/W\# = 1, E = 1, RS = 0

AL,5

001E EE

OUT

DX.AL

001F 90

NOP

;delay to allow access

0020 90

NOP

0021 BA 0300

MOV

DX. PORTA

;select port A

0024 EC

IN

AL, DX

;get status of busy flag

```

| 0026 BA 0301 MOV DX,PORTB 0029 B0 00 MOV AL,0 002B EE OUT DX,AL 002C BA 0303 MOV DX,CMD8255 002F B0 80 MOV AL,80H 0031 EE OUT DX,AL 0032 58 POP AX 0033 D0 E0 SHL AL,1 .UNTIL !CARRY? ;until not bu. | 0025 | 50 |      |      | PUSH            | I AX       |        |     |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|------|------|-----------------|------------|--------|-----|------|

| 002B EE OUT DX,AL 002C BA 0303 MOV DX,CMD8255 002F B0 80 MOV AL,80H 0031 EE OUT DX,AL 0032 58 POP AX 0033 D0 E0 SHL AL,1 .UNTIL !CARRY? ;until not but                                               | 0026 | BA | 0301 |      | MOV             | DX, PORTB  |        |     |      |

| 002C BA 0303 MOV DX,CMD8255<br>002F B0 80 MOV AL,80H<br>0031 EE OUT DX,AL<br>0032 58 POP AX<br>0033 D0 E0 SHL AL,1<br>.UNTIL !CARRY? ;until not but                                                  | 0029 | B0 | 00   |      | MOV             | AL,0       |        |     |      |

| 002F B0 80 MOV AL,80H<br>0031 EE OUT DX,AL<br>0032 58 POP AX<br>0033 D0 E0 SHL AL,1<br>.UNTIL !CARRY? ;until not but                                                                                 | 002B | EE |      |      | OUT             | DX,AL      |        |     |      |

| 0031 EE OUT DX,AL 0032 58 POP AX 0033 D0 E0 SHL AL,1 .UNTIL !CARRY? ;until not bu                                                                                                                    | 002C | BA | 0303 |      | MOV             | DX,CMD8255 |        |     |      |

| 0032 58 POP AX 0033 D0 E0 SHL AL,1 .UNTIL !CARRY? ;until not bu                                                                                                                                      | 002F | B0 | 80   |      | VOM             | AL,80H     |        |     |      |

| 0033 D0 E0 SHL AL,1 .UNTIL !CARRY? ;until not bu                                                                                                                                                     | 0031 | EE |      |      | OUT             | DX,AL      |        |     |      |

| .UNTIL !CARRY? ;until not bu                                                                                                                                                                         | 0032 | 58 |      |      | POP             | AX         |        |     |      |

| , und 1 100 Du                                                                                                                                                                                       | 0033 | D0 | E0   |      | SHL             | AL,1       |        |     |      |

| 0037 C3 RET                                                                                                                                                                                          |      |    |      | . Մ  | $\mathtt{NTIL}$ | !CARRY?    | ;until | not | busy |

|                                                                                                                                                                                                      | 0037 | C3 |      | RE'  | T               |            |        |     |      |

| 0038 BUSY ENDP                                                                                                                                                                                       | 0038 |    |      | BUSY | ENDP            | •          |        |     |      |

Once the BUSY procedure is available, data can be sent to the display by writing another procedure called WRITE. The WRITE procedure uses BUSY to test before trying to write new data to the display. Example 10–12 shows the WRITE procedure, which transfers the ASCII character from the BL register to the current cursor position of the display. Note that the initialization dialog has sent the cursor for auto-increment, so if WRITE is called more than once, the characters written to the display will appear one next to the other, as they would on a video display.

TABLE 10-3 Instructions for most Optrex LCD displays.

| Instruction            | Code      | Description                                                                              | Execution Time |  |

|------------------------|-----------|------------------------------------------------------------------------------------------|----------------|--|

| Clear display          | 0000 0001 | Clears display and homes the cursor                                                      | 1.64 ms        |  |

| Cursor home            | 0000 0010 | Homes the cursor                                                                         | 1.64 ms        |  |

| Entry mode set         | 0000 0AS  | Sets cursor movement direction (A=1 increment) and shift (S=1 shift)                     | 40 μs          |  |

| Display on/off         | 0000 1DCB | Sets display on/off<br>(D=1 on) (C=1 cursor on)<br>(B=1 cursor blink)                    | <b>40</b> μs   |  |

| Cursor/display shift   | 0001 SR00 | Sets cursor movement and display shift (S=1 shift display) (S=0 move cursor) (R=1 right) | <b>4</b> 0 μs  |  |

| Function set 001L NF00 |           | Programs chip (L=1 8-bit,<br>L=0 4-bits) (N=1 2 lines)<br>(F=1 5x10, F=0 5x7)            | 40 μs          |  |

| Set CGRAM address      | 01XX XXXX | Sets character generator RAM address                                                     | 40 μs          |  |

| Set DRAM address       | 10XX XXXX | Sets display RAM address                                                                 | 40 μs          |  |

| Read busy flag         | B000 0000 | Reads busy flag (B=1 busy)                                                               | 0              |  |

| Write data             | Data      | Writes data to display or character generator RAM                                        | 40 μs          |  |

| Read data              | Data      | Reads data from display or character generator RAM                                       | 40 μs          |  |

### **EXAMPLE 10-12**

```

;procedure that writes the ASCII contents of the BL

;register to the display

003A

WRITE PROC

NEAR

MOV

DX,CMD8255

003A BA 0303

AL,80H

MOV

003D B0 80

DX, AL

OUT

003F EE

:data to port A

DX. PORTA

0040 BA 0300

MOV

0043 8A C3

MOV

AL,BL

OUT

DX,AL

0045 EE

MOV

DX, PORTB

0046 BA 0301

;RS = 1, R/W# = 0, E = 0

0049 B0 02

MOV

AL, 2

OUT

DX,AL

004B EE

NOP

004C 90

NOP

004D 90

;RS = 1, R/W# = 0, E = 1

AL. 6

004E B0 06

MOV

OUT

DX, AL

0050 EE

0051 90

NOP

NOP

0052 90

;RS = 0, R/W# = 0, E = 0

AL. 0

MOV

0053 B0 00

OUT

DX.AL

0055 EE

;wait for LCD

BUSY

0056 E8 FFB7

CALL

RET

0059 C3

WRITE ENDP

005A

```

The only other procedure that is needed for a basic display is the clear and home cursor procedure called CLS, shown in Example 10–13. With CLS and the procedures presented thus far, you can display any message on the display, clear it, display another message, and basically operate the display. As mentioned earlier, the clear command requires a time delay (at least 1.64 ms) instead of a call to BUSY for proper operation. In this procedure, we used the 4.1 ms time delay.

### **EXAMPLE 10-13**

```

;procedure to clear the display and home the cursor

NEAR

CLS

PROC

005A

DX, CMD8255

005A BA 0303

MOV

005D B0 80

MOV

AL, 80H

OUT

DX,AL

005F EE

DX, PORTA

0060 BA 0300

MOV

;clear instruction

0063 B0 01

MOV

AL.1

DX.AL

0065 EE

OUT

MOV

DX, PORTB

0066 BA 0301

;RS = 0, R/W# = 0, E = 1

AL,4

0069 B0 04

MOV

OUT

DX, AL

006B EE

006C 90

NOP

006D 90

NOP

;RS = 0, R/W# = 0, E = 0

MOV

AL,0

006E B0 00

DX,AL

0070 EE

OUT

DELAY41

CALL

0071 E8 0044

0074 C3

RET

0075

CLS

ENDP

```

Additional procedures that could be developed might select a display RAM position. The display RAM address starts at 0 and progresses across the display until the last character address on the first line is location 19, location 20 is the first display position of the second line, and so forth. Once you can move the display address, you can change individual characters on the display and even read data from the display. These procedures are for you to develop if they are needed.

A word about the display RAM inside of the LCD display. The LCD contains 128 bytes of memory, addresssed from 00H to 7FH. Not all of this memory is used. For example, the one-line × 20-character display uses only the first 20 bytes of memory (00H-13H.) The first line of any of these displays always starts at address 00H. The second line of any display powered by the HD44780 always begins at address 40H. For example, a two-line × 40-character display uses addresses 00H-27H to store ASCII-coded data from the first line. The second line is stored at addresses 40H-67H for this display. In the four-line displays, the first line is at 00H, the second is at 40H, the third is at 14H, and the last line is at 54H. The largest display device that uses the HD44780 is a two-line × 40-character display. The four-line by 40-character display uses an M50530 or a pair of HD44780s. Because information on these devices can be readily found on the Internet, they are not covered in the text

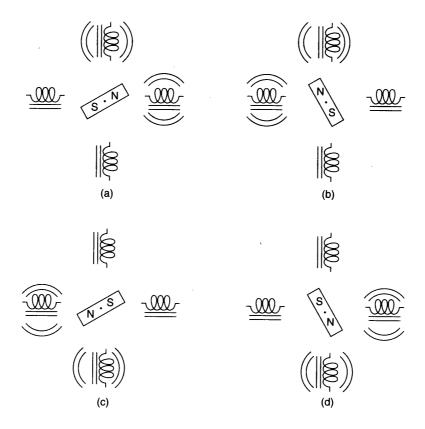

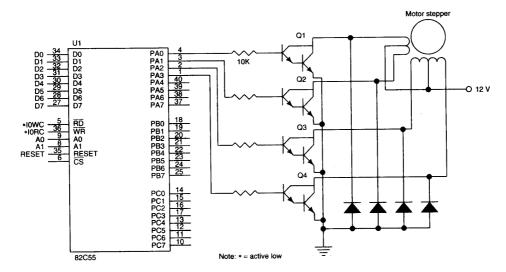

A Stepper Motor Interfaced to the 82C55. Another device often interfaced to a computer system is the stepper motor. A stepper motor is a digital motor because it is moved in discrete steps as it traverses through 360\$ A common stepper motor is geared to move perhaps 15\$per step in an inexpensive stepper motor, to 1\$per step in a more costly high-precision stepper motor. In all cases, these steps are gained through many magnetic poles and/or gearing. Notice that two coils are energized in Figure 10-22. If less power is required, one coil may be energized at a time, causing the motor to step at 45\$ 135\$ 225\$ and 315\$

Figure 10-22 shows a four-coil stepper motor that uses an armature with a single pole. Notice that the stepper motor is shown four times with the armature (permanent magnetic) rotated to four discrete places. This is

**FIGURE 10–22** The stepper motor showing full-step operation. (a) 45° (b) 135° (c) 225° (d) 315°.

A stepper motor interfaced to the 82C55. This illustration does not show FIGURE 10-23 the decoder.

accomplished by energizing the coils, as shown. This is an illustration of full stepping. The stepper motor is driven by using NPN Darlington amplifier pairs to provide a large current to each coil.

A circuit that can drive this stepper motor is illustrated in Figure 10-23, with the four coils shown in place. This circuit uses the 82C55 to provide it with the drive signals that are used to rotate the armature of the motor in either the right-hand or left-hand direction.

A simple procedure that drives the motor (assuming that port A is programmed in mode 0 as an output device) is listed in Example 10-14. This subroutine is called, with CX holding the number of steps and direction of the rotation. If CX > 8000H, the motor spins in the right-hand direction; if CX < 8000H, it spins in the left-hand direction. The leftmost bit of CX is removed and the remaining 15 bits contain the number of steps. Notice that the procedure uses a time delay (not illustrated) that causes a 1 ms time delay. This time delay is required to allow the stepper-motor armature time to move to its next position.

### **EXAMPLE 10-14**

| 2042            | DODE FOIL   | 40H          | assign Port A            |

|-----------------|-------------|--------------|--------------------------|

| = 0040          | PORT EQU    | 4011         | , assign fold A          |

|                 | ;A procedur | e to control | stepper motor.           |

| 0000            | STEP PROC   | NEAR         |                          |

| 0000 A0 0000 R  | MOV         | AL, POS      | ;get position            |

| 0003 81 F9 8000 | CMP         | CX,8000H     |                          |

| 0007 77 10      | JA          | RH           | ;if right-hand direction |

| 0009 83 F9 00   | CMP         | CX,0         |                          |

| 000C 74 14      | JE          | STEP_OUT     | ;if no steps             |

| 000E            | STEP1:      |              |                          |

| 000E D0 C0      | ROL         | AL,1         | ;step left               |

| 0010 E6 40      | OUT         | PORT, AL     |                          |

| 0012 E8 0011    | CALL        | DELAY        | ;wait one millisecond    |

| 0015 E2 F7      | LOOP        | STEP1        | ;repeat until CX = 0     |

| 0017 EB 09      | JMP         | STEP_OUT     |                          |

| 0019 |            | RH:       |          |                       |

|------|------------|-----------|----------|-----------------------|

| 0019 | 81 E1 7FFF | AND       | CX,7FFFH | clear bit 15;         |

| 001D |            | RH1:      |          |                       |

| 001D | D0 C8      | ROR       | AL,1     | ;step right           |

| 001F | E6 40      | OUT       | PORT, AL |                       |

| 0021 | E8 0006    | CALL      | DELAY    | ;wait one millisecond |

| 0024 | E2 F7      | LOOP      | RH1      | ;repeat until CX = 0  |

| 0026 |            | STEP_OUT: |          |                       |

| 0026 | A2 0000    | VOM       | POS,AL   | ;save position        |

| 0029 | C3         | RET       |          | _                     |

|      |            |           |          |                       |

|      |            |           |          |                       |

| 0029 |            | STEP ENDP |          |                       |

The current position is stored in memory location POS, which must be initialized with 33H, 66H, 0CCH, or 99H. This allows a simple ROR (step right) or ROL (step left) instruction to rotate the binary bit pattern for the next step.

Stepper motors can also be operated in the half-step mode, which allows eight steps per sequence. This is accomplished by using the full-step sequence described with a half step obtained by energizing one coil interspersed between the full steps. Half-stepping allows the armature to be positioned at 0.\$90\$ 180\\$ and 270\\$ The half-step position codes are 11H, 22H, 44H, and 88H. A complete sequence of eight steps would follow as: 11H, 33H, 22H, 66H, 44H, 0CCH, 88H, and 99H. This sequence could be either output from a lookup table or generated with software.

**Key Matrix Interface.** Keyboards come in a vast variety of sizes, from the standard 101-key QWERTY keyboards interfaced to the microprocessor to small specialized keyboards that may contain only four to 16 keys. This section of the text concentrates on the smaller keyboards that may be purchased preassembled or may be constructed from individual key switches.

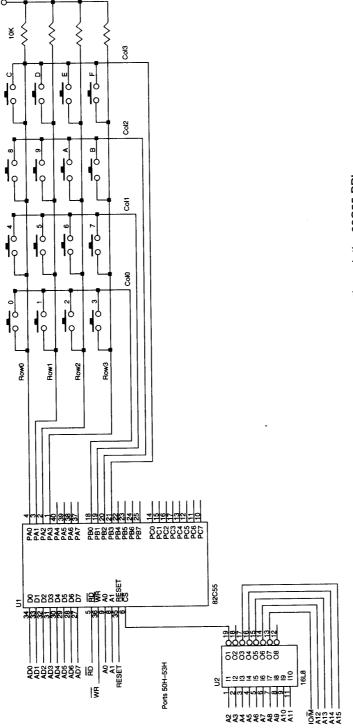

Figure 10–24 illustrates a small key-matrix that contains 16 switches interfaced to ports A and B of an 82C55. In this example, the switches are formed into a  $4 \times 4$  matrix, but any matrix could be used such as a  $2 \times 8$ . Notice how the keys are organized into four rows (ROW0–ROW3) and four columns (COL0–COL3). Each row is connected to 5.0 V through a 10 K\* pull-up resistor to ensure that the row is pulled high when no push-button switch is closed.

The 82C55 is decoded (PAL program is not shown) at I/O ports 50H–53H for an 8088 microprocessor. Port A is programmed as an input port to read the rows and port B is programmed as an output port to select a column. For example, if 1110 is output to port B pins PB3–PB0, column 0 has a logic 1, so the four keys in column 0 are selected. Notice that with a logic 0 on PB0, the only switches that can place a logic 0 onto port A are switches 0–3. If switches 4–F are closed, the corresponding port A pins remain a logic 1. Likewise, if a 1101 is output to port B, switches 4–7 are selected, and so forth.

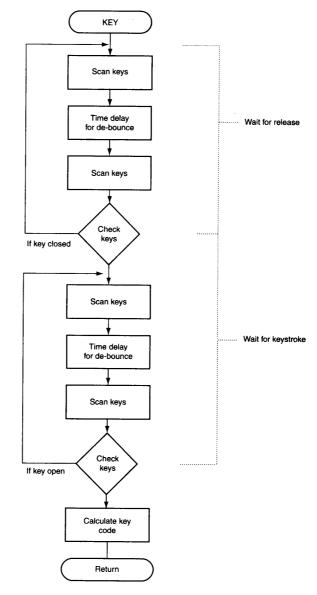

A flowchart of the software required to read a key from the keyboard matrix and de-bounce the key is illustrated in Figure 10–25. Keys must be de-bounced, which is normally accomplished with a short time delay of from 10–20 ms. The flowchart contains three main sections. The first waits for the release of a key. This seems awkward, but software executes very quickly in a microprocessor and there is a possibility that the program will return to the top of this program before the key is released, so we must wait for a release first. Next, the flowchart shows that we wait for a keystroke. Once the keystroke is detected, the position of the key is calculated in the final part of the flowchart.

The software uses a procedure called SCAN to scan the keys and another called DELAY to waste 10 ms of time for de-bouncing. The main keyboard procedure is called KEY and it appears with the others in Example 10–15. Note that the SCAN procedure is generic, so it can handle any keyboard configuration from a  $2 \times 2$  matrix to an  $8 \times 8$  matrix. Changing the two equates at the start of the program (ROW and COL) will change the configuration of the software for any size keyboard. Also note that the steps required to initialize the 82C55 so that port A is an input port and port B is an output port are not shown.

**FIGURE 10–24** A 4  $\times$  4 keyboard matrix connected to an 8088 microprocessor through the 82C55 PPI.

FIGURE 10-25 The flowchart of a keyboard-scanning procedure.

### EXAMPLE 10-15

;A keyboard procedure that scans the keyboard and ; returns with the numeric code of the key in AL.

|        | ,                  |                    |

|--------|--------------------|--------------------|

| = 0004 | ROWS EQU 4         | ;number of rows    |

| = 0004 | COLS EQU 4         | ;number of columns |

| = 0050 | PORTA EQU 50H      | ;port A address    |

| = 0051 | PORTB EQU 51H      | port B address;    |

|        |                    |                    |

| 0000   | KEY PROC NEAR USES | CX                 |

### 314 CHAPTER 10 BASIC I/O INTERFACE

| 0001                 | E8 | 002F       |          | CALL       | SCAN         | ;test all keys              |

|----------------------|----|------------|----------|------------|--------------|-----------------------------|

| 0004                 | 75 | FA         |          | JNZ        | KEY          | ;if key closed              |

| 0006                 | E8 | 0048       |          | CALL       | DELAY        | ;wait for about 10 ms       |

| 0009                 | E8 | 0027       |          | CALL       | SCAN         | ;test all keys              |

| 000C                 | 75 | F2         |          | JNZ        | KEY          | ;if key closed .            |

| 000E                 |    |            | KEY1:    |            |              |                             |

| 000E                 |    | 0022       |          | CALL       | SCAN         | ;test all keys              |

| 0011                 |    | FB         |          | JZ         | KEY1         | ; if no key closed          |

| 0013                 |    | 003B       |          | CALL       | DELAY        | ;wait for about 10 ms       |

| 0016                 |    | 001A       |          | CALL       | SCAN         | ;test all keys              |

| 0019                 |    | F3         |          | JZ         | KEY1         | ; if no key closed          |

| 001B                 | 50 |            |          | PUSH       | AX           | ; save row codes            |

| 001C                 |    | 04         |          | MOV        | AL, COLS     | ;calculate starting row key |

| 001E                 |    | C1         |          | SUB        | AL,CL        |                             |

| 0020                 |    | 04         |          | MOV        | CH, ROWS     |                             |

| 0022                 |    | E5         |          | MUL        | CH           |                             |

| 002 <b>4</b><br>0026 |    | C8<br>C9   |          | MOV<br>DEC | CL,AL<br>CL  |                             |

|                      | 58 | C9         |          | POP        | AX           |                             |

| 0028<br>0029         | 56 |            | KEY2:    | POP        | AA           |                             |

| 0029                 | DΩ | C8         | KEIZ:    | ROR        | AL,1         | ;find row position          |

| 0029<br>002B         |    | C1         |          | INC        | CL CL        | , IIIId Iow pobleton        |

| 002B                 |    | FA         |          | JC         | KEY2         |                             |

| 002B                 |    | C1         |          | MOV        | AL,CL        | ; mode code to AL           |

| 0021                 | OA | C1         |          | RET        | 111,01       | ,                           |

|                      |    |            |          |            |              |                             |

| 0033                 |    |            | KEY      | ENDP       |              |                             |

| 0033                 |    |            | SCAN     | PROC       | NEAR USES BX |                             |

| 0034                 | В1 | 04         |          | MOV        | CL, ROWS     | ;form row mask              |

| 0036                 | в7 | FF         |          | MOV        | BH,0FFH      |                             |

| 0038                 | D2 | <b>E</b> 7 |          | SHL        | BH,CL        |                             |

| 003A                 |    | 0004       |          | VOM        | CX, COLS     | ;load column count          |

| 003D                 | В3 | FE         |          | MOV        | BL,0FEH      | get selection code;         |

| 003F                 |    |            | SCAN1    |            |              |                             |

| 003F                 |    | C3         |          | MOV        | AL,BL        | ;select column              |

| 0041                 |    | 51         |          | OUT        | PORTB, AL    |                             |

| 0043                 |    | C3         |          | ROL        | BL,1         |                             |

| 0045                 |    | 50         |          | IN         | AL, PORTA    | read rows;                  |

| 0047                 |    | C7         |          | OR         | AL, BH       | test for a hou              |

| 0049                 |    | FF         |          | CMP        | AL, OFFH     | ;test for a key             |

| 004B                 |    | 02         |          | JNZ        | SCAN2        |                             |

| 004D                 | ΕZ | F0         | SCAN2    | LOOP       | SCAN1        |                             |

| 004F                 |    |            | SCANZ    | RET        |              |                             |

|                      |    |            |          |            |              |                             |

| 0051                 |    |            | SCAN     | ENDP       |              |                             |

| 0051                 |    |            | DELAN    | DROG       | MEAD HEEC CV |                             |

| 0051                 |    |            | DELAY    | PROC       | NEAR USES CX |                             |

| 0052                 | В9 | 1388       |          | MOV        | CX,5000      | ;10ms (8MHz clock)          |

| 0055                 |    |            | DELAY    | 1:         |              |                             |

| 0055                 | E2 | FE         |          | LOOP       | DELAY1       |                             |

|                      |    |            |          | RET        |              |                             |

| 0059                 |    |            | יי אים ח | ENDP       |              |                             |

| 0059                 |    |            | DELIAI   | EMDE       |              |                             |

A note about the SCAN procedure. The time between where the keyboard column is selected and where the rows are read is very short. In a very high-speed system, a small time delay must be placed between these two points for the data at port A to settle to its final state. In most cases, this is not needed—the SCAN procedure should not scan the display at a rate higher than 30 KHz. If it does, the Federal Communications Commission (FCC) will not approve its application in any accepted system.

## **Mode 1 Strobed Input**

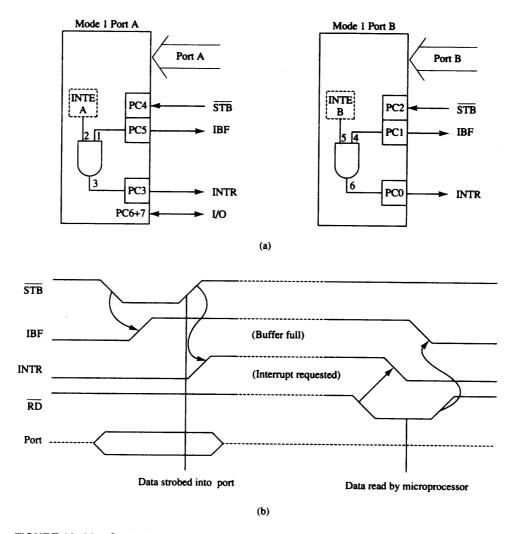

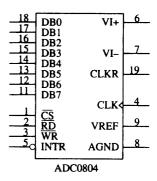

Mode 1 operation causes port A and/or port B to function as latching input devices. This allows external data to be stored into the port until the microprocessor is ready to retrieve it. Port C is also used in mode 1 operation—not for data, but for control or handshaking signals that help operate either or both port A and port B as strobed input ports. Figure 10–26 shows how both ports are structured for mode 1 strobed input operation and the timing diagram.

The strobed input port captures data from the port pins when the strobe (STB) is activated. Note that the strobe captures the port data on the 0-to-1 transition. The STB signal causes data to be captured in the port and it activates the IBF (**input buffer full**) and INTR (**interrupt request**) signals. Once the microprocessor, through software (IBF) or hardware (INTR), notices that data are strobed into the port, it executes an IN instruction to read the port (RD). The act of reading the port restores both IBF and INTR to their inactive states until the next datum is strobed into the port.

**FIGURE 10–26** Strobed input operation (mode 1) of the 82C55. (a) Internal structure and (b) timing diagram.

### Signal Definitions for Mode 1 Strobed Input

STB The strobe input loads data into the port latch, which holds the information until it is

input to the microprocessor via the IN instruction.

**IBF** Input buffer full is an output indicating that the input latch contains information.

INTR Interrupt request is an output that requests an interrupt. The INTR pin becomes a

logic 1 when the STB input returns to a logic 1, and is cleared when the data are input

from the port by the microprocessor.

INTE The interrupt enable signal is neither an input nor an output; it is an internal bit

programmed via the port PC4 (port A) or PC2 (port B) bit position.

**PC7**, **PC6** The port C pins 7 and 6 are general-purpose I/O pins that are available for any purpose.

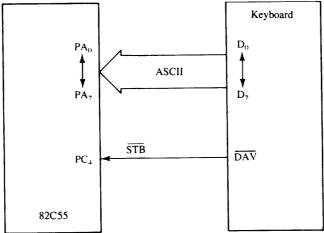

Strobed Input Example. An excellent example of a strobed input device is a keyboard. The keyboard encoder de-bounces the key-switches, and provides a strobe signal whenever a key is depressed and the data output contain the ASCII-coded key code. Figure 10–27 illustrates a keyboard connected to strobed input port A. Here DAV (data available) is activated for 1.0 ③ each time that a key is typed on the keyboard. This causes data to be strobed into port A because DAV is connected to the STB input of port A. Each time a key is typed, therefore, it is stored into port A of the 82C55. The STB input also activates the IBF signal, indicating that data are in port A.

Example 10–16 shows a procedure that reads data from the keyboard each time a key is typed. This procedure reads the key from port A and returns with the ASCII code in AL. To detect a key, port C is read and the IBF bit (bit position PC5) is tested to see whether the buffer is full. If the buffer is empty (IBF = 0), then the procedure keeps testing this bit, waiting for a character to be typed on the keyboard.

### **EXAMPLE 10-16**

;A procedure that reads the keyboard encoder ; and returns the ASCII character in  ${\rm AL}\,.$

BIT5 EQU 20H PORTC EQU 22H

= 0020= 0022

PORTC EQU 22H

**FIGURE 10–27** Using the 82C55 for strobed input operation of a keyboard.

| = 0020                               | )                          |          | PORTA | EQU                           | 20H                                        |                                                          |

|--------------------------------------|----------------------------|----------|-------|-------------------------------|--------------------------------------------|----------------------------------------------------------|

| 0000                                 |                            |          | READ  | PROC                          | NEAR                                       |                                                          |

| 0000<br>0002<br>0004<br>0006<br>0008 | E4<br>A8<br>74<br>E4<br>C3 | 20<br>FA |       | IN<br>TEST<br>JZ<br>IN<br>RET | AL, PORTC<br>AL, BIT5<br>READ<br>AL, PORTA | <pre>;read Port C ;test IBF ;if IBF = 0 ;read data</pre> |

| 0009                                 |                            |          | READ  | ENDP                          |                                            |                                                          |

# **Mode 1 Strobed Output**

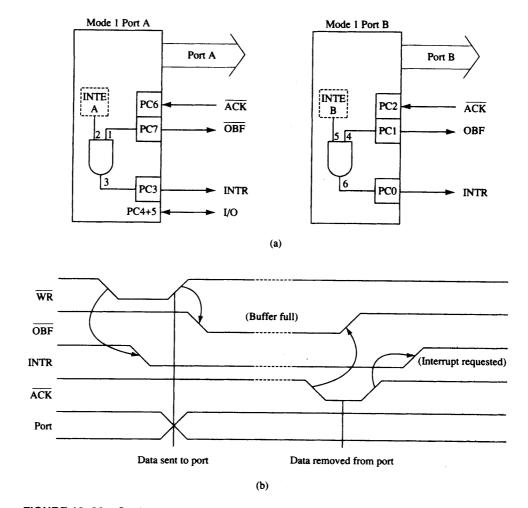

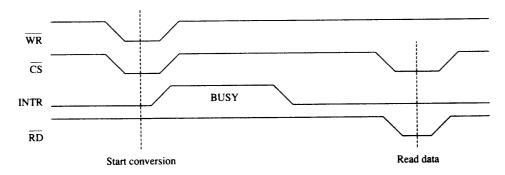

Figure 10–28 illustrates the internal configuration and timing diagram of the 82C55 when it is operated as a strobed output device under mode 1. Strobed output operation is similar to mode 0 output operation, except that control signals are included to provide handshaking.

**FIGURE 10–28** Strobed output operation (mode 1) of the 82C55. (a) Internal structure and (b) timing diagram.

Whenever data are written to a port programmed as a strobed output port, the OBF (output buffer full) signal becomes a logic 0 to indicate that data are present in the port latch. This signal indicates that data are available to an external I/O device that removes the data by strobing the  $\overline{ACK}$  (acknowledge) input to the port. The  $\overline{ACK}$  signal returns the OBF signal to a logic 1, indicating that the buffer is not full.

### Signal Definitions for Mode 1 Strobed Output

**ACK**

| OBF | Output buffer full is an output that goes low whenever data are output (OUT) to the    |

|-----|----------------------------------------------------------------------------------------|

|     | port A or port B latch. This signal is set to a logic 1 whenever the ACK pulse returns |

|     | from the external device.                                                              |

The **acknowledge** signal causes the OBF pin to return to a logic 1 level. The ACK is a

response from an external device, indicating that it has received the data from the

82C55 port.

INTR Interrupt request is a signal that often interrupts the microprocessor when the external

device receives the data via the ACK signal. This pin is qualified by the internal INTE

(interrupt enable) bit.

**INTE** Interrupt enable is neither an input nor an output; it is an internal bit programmed to

enable or disable the INTR pin. The INTE A bit is programmed as PC6 and INTE B is

programmed as PC2.

PC5, PC4 Port C pins 5 and 4 are general-purpose I/O pins. The bit set and reset command may be

used to set or reset these two pins.

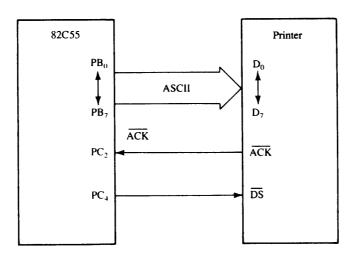

**Strobed Output Example.** The printer interface discussed in Section 10–1 is used here to demonstrate how to achieve strobed output synchronization between the printer and the 82C55. Figure 10–29 illustrates port B connected to a parallel printer, with eight data inputs for receiving ASCII-coded data, a DS (**data strobe**) input to strobe data into the printer, and an ACK output to acknowledge the receipt of the ASCII character.

In this circuit, there is no signal to generate the DS signal to the printer, so PC4 is used with software that generates the DS signal. The ACK signal that is returned from the printer acknowledges the receipt of the data and is connected to the ACK input of the 82C55.

**FIGURE 10–29** The 82C55 connected to a parallel printer interface that illustrates the strobed output mode of operation for the 82C55.

Example 10–17 lists the software that sends the ASCII-coded character in AH to the printer. The procedure first tests OBF to decide whether the printer has removed the data from port B. If not, the procedure waits for the ACK signal to return from the printer. If OBF = 1, then the procedure sends the contents of AH to the printer through port B and also sends the DS signal.

### EXAMPLE 10-17

|                          | ;from<br>;    | AH to      | the printer v     | rs the ASCII character<br>ia port B. |

|--------------------------|---------------|------------|-------------------|--------------------------------------|

| = 0002<br>= 0062         | BIT1<br>PORTC | EQU        | 2<br>62H          |                                      |

| = 0061                   | PORTE         |            | 61H               |                                      |

| = 0063                   | CMD           | EQU        | 63H               |                                      |

| 0000                     | PRINT         | PROC       | NEAR              |                                      |

|                          | ;checl        | k prin     | ter ready         |                                      |

| 0000 E4 62               |               | IN         | AL, PORTC         | ;get OBF                             |

| 0002 A8 02<br>0004 74 FA |               | TEST<br>JZ | AL, BIT1<br>PRINT | <pre>;test OBF ;if OBF = 0</pre>     |

|                          | ;send         | chara      | cter to printe    | r                                    |

| 0006 8A C4               |               | MOV        | AL,AH             | ;get data                            |

| 0008 E6 61               |               | OUT        | PORTB, AL         | ;print data                          |

|                          | ;send         | data :     | strobe to prin    | ter                                  |

| 000A B0 08               |               | MOV        | AL,8              | ;clear DS                            |

| 000C E6 63               |               | OUT        | CMD, AL           |                                      |

| 000E B0 09<br>0010 E6 63 |               | VOM        | AL,9<br>CMD,AL    | ;set DS                              |

| 0010 E0 03               |               | RET        | CHD, AL           |                                      |

| 0013                     | PRINT         | ENDP       |                   |                                      |

## **Mode 2 Bi-directional Operation**

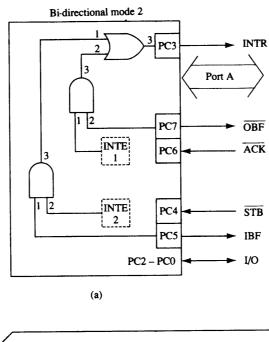

In mode 2, which is allowed with group A only, port A becomes bi-directional, allowing data to be transmitted and received over the same eight wires. Bi-directional bused data are useful when interfacing two computers. It is also used for the IEEE-488 parallel high-speed GPIB (**general purpose instrumentation bus**) interface standard. Figure 10-30 shows the internal structure and timing diagram for mode 2 bi-directional operation.

## Signal Definitions for Bi-directional Mode 2

| INTR | <b>Interrupt request</b> is an output used to interrupt the microprocessor for both input and output conditions.                                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OBF  | Output buffer full is an output indicating that the output buffer contains data for the bi-<br>directional bus.                                                                             |

| ACK  | <b>Acknowledge</b> is an input that enables the three-state buffers so that data can appear on port A. If ACK is a logic 1, the output buffers of port A are at their high-impedance state. |

| STB  | The <b>strobe</b> input loads the port A input latch with external data from the bi-directional port A bus.                                                                                 |

| IBF  | <b>Input buffer full</b> is an output used to signal that the input buffer contains data for the external bi-directional bus.                                                               |

FIGURE 10-30 Mode 2 operation of the 82C55. (a) Internal structure and (b) timing diagram.

INTE

Interrupt enable are internal bits (INTE1 and INTE2) that enable the INTR pin. The state of the INTR pin is controlled through port C bits PC6 (INTE1) and PC4 (INTE2).

PC2, PC1, and PC0

These pins are general-purpose I/O pins in mode 2 controlled by the bit set and reset command.

The bi-directional bus is used by referencing port A with the IN and OUT instructions. To The Bi-directional Bus. transmit data through the bi-directional bus, the program first tests the OBF signal to determine whether the output buffer is empty. If it is, then data are sent to the output buffer via the OUT instruction. The external circuitry also monitors the OBF signal to decide whether the microprocessor has sent data to the bus. As soon as the output circuitry sees a logic 0 on OBF, it sends back the ACK signal to remove it from the output buffer. The ACK signal sets the OBF bit and enables the three-state output buffers so that data may be read. Example 10–18 lists a procedure that transmits the contents of the AH register through bi-directional port A.

### **EXAMPLE 10-18**

```

;A procedure that transmits AH through the bi-

; directional bus of port A.

= 0080

BIT7 EQU

80H

= 0062

PORTC EQU

62H

= 0060

PORTA EQU

60H

0000

TRANS PROC

NEAR

0000

E4 62

IN

AL, PORTC

;get OBF

0002

A8 80

TEST

AL,BIT7

;test OBF

0004

74 FA

JΖ

TRANS

; if OBF = 1

0006

8A C4

MOV

AL, AH

; get data

0008

E6 60

OUT

PORTA, AL

;send data

A000

C3

RET

000B

TRANS ENDP

```

To receive data through the bi-directional port A bus, the IBF bit is tested with software to decide whether data have been strobed into the port. If IBF = 1, then data are input using the IN instruction. The external interface sends data into the port by using the STB signal. When STB is activated, the IBF signal becomes a logic 1 and the data at port A are held inside the port in a latch. When the IN instruction executes, the IBF bit is cleared and the data in the port are moved into AL. Example 10–19 lists a procedure that reads data from the port.

### **EXAMPLE 10-19**

|                                                                 | ;dire                  |                               |                                            | data from the bi-<br>returns it in AL.              |

|-----------------------------------------------------------------|------------------------|-------------------------------|--------------------------------------------|-----------------------------------------------------|

| = 0020<br>= 0062<br>= 0060                                      | BIT5<br>PORTC<br>PORTA | ~ -                           | 20н<br>62н<br>60н                          |                                                     |

| 0000                                                            | READ                   | PROC                          | NEAR                                       |                                                     |

| 0000 E4 62<br>0002 A8 20<br>0004 74 FA<br>0006 E4 60<br>0008 C3 |                        | IN<br>TEST<br>JZ<br>IN<br>RET | AL, PORTC<br>AL, BIT5<br>READ<br>AL, PORTA | <pre>;get IBF ;test IBF ;if IBF = 0 ;get data</pre> |

| 0009                                                            | READ                   | ENDP                          |                                            |                                                     |

The INTR (**interrupt request**) pin can be activated from both directions of data flow through the bus. If INTR is enabled by both INTE bits, then the output and input buffers both cause interrupt requests. This occurs when data are strobed into the buffer using STB or when data are written using OUT.

## 82C55 Mode Summary

Figure 10–31 shows a graphical summary of the three modes of operation for the 82C55. Mode 0 provides simple I/O, mode 1 provides strobed I/O, and mode 2 provides bi-directional I/O. As mentioned, these modes are selected through the command register of the 82C55.

|        |                                      | Mode 0 |     | Mo                                                                                                              | Mode 2                                                                                                          |                                  |

|--------|--------------------------------------|--------|-----|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|

| Port A |                                      | IN     | OUT | IN                                                                                                              | OUT                                                                                                             | I/O                              |

| Port B |                                      | IN     | OUT | IN                                                                                                              | OUT                                                                                                             | Not<br>used                      |

| Port C | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | IN     | OUT | INTR <sub>B</sub> IBF <sub>B</sub> STB <sub>B</sub> INTR <sub>A</sub> STB <sub>A</sub> IBF <sub>A</sub> I/O I/O | INTR <sub>B</sub> OBF <sub>B</sub> ACK <sub>B</sub> INTR <sub>A</sub> I/O I/O ACK <sub>A</sub> OBF <sub>A</sub> | I/O I/O I/O INTR STB IBF ACK OBF |

FIGURE 10-31 A summary of the port connections for the 82C55 PPI.

#### THE 8279 PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE 10-4

The 8279 is a programmable keyboard and display interfacing component that scans and encodes up to a 64-key keyboard and controls up to a 16-digit numerical display. The keyboard interface has a built-in first-in, first-out (FIFO) buffer that allows it to store up to eight keystrokes before the microprocessor must retrieve a character. The display section controls up to 16 numeric displays from an internal 16 x 8 RAM that stores the coded display information.

### **Basic Description of the 8279**

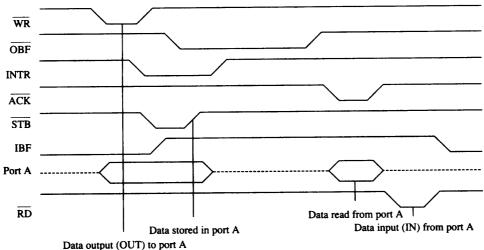

As we shall see, the 8279 is designed to easily interface with any microprocessor. Figure 10-32 illustrates the pinout of this device. The definition of each pin connection follows.

### Pin Definitions for the 8279

The A0 address input selects data or control for reads and writes between the A0

microprocessor and the 8279. A logic 0 selects data and a logic 1 selects control or

status register.

BD Blank is an output used to blank the displays.

Clock is an input that generates the internal timing for the 8279. The maximum **CLK**

> allowable frequency on the CLK pin is 3.125 MHz for the 8279-5 and 2.0 MHz for the 8279. Other timings require wait states in microprocessors executing at above 5 MHz.

Control/strobe is an input normally connected to the Control key on a keyboard. CN/ST **CS**

Chip select is an input that enables the 8279 for programming, reading the keyboard and status information, and writing control and display data.

DB7-DB0 The data bus consists of bi-directional pins that connect to the data bus on the

microprocessor.

Interrupt request is an output that becomes a logic 1 whenever a key is pressed on the IRO

keyboard. This signal indicates that keyboard data are available for the microprocessor.

Outputs that send data to the displays (most-significant). **OUTA3-OUTA0**

**FIGURE 10–32** The pin-out and logic symbol of the 8279 programmable keyboard/display interface. (Courtesy of Intel Corporation.)

| OUTB3-OUTB0 | Outputs that send data to the displays (least-significant).                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD          | The <b>read</b> input is directly connected to the IORC or RD signal from the system. The RD input causes, when CS is a logic 0, a read from the data registers or status register.                                       |

| RESET       | The <b>reset</b> input connects to the system RESET signal.                                                                                                                                                               |

| RL7-RL0     | Return lines are inputs used to sense any key depression in the keyboard matrix.                                                                                                                                          |

| SHIFT       | The shift input normally connects to the Shift key on a keyboard.                                                                                                                                                         |

| SL3-SL0     | The scan line outputs scan both the keyboard and the displays.                                                                                                                                                            |

| WR          | <b>Write</b> is an input that connects to either the write strobe signal that is developed with external logic. The WR input causes data to be written to either the data registers or control registers within the 8279. |

| Vcc         | A power supply pin connected to the system +5.0 V bus.                                                                                                                                                                    |

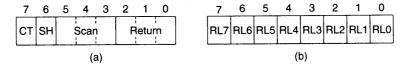

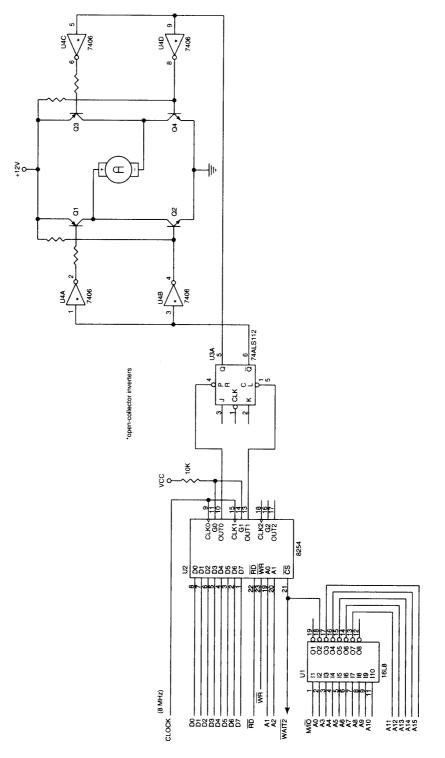

## Interfacing the 8279 to the Microprocessor

Vss

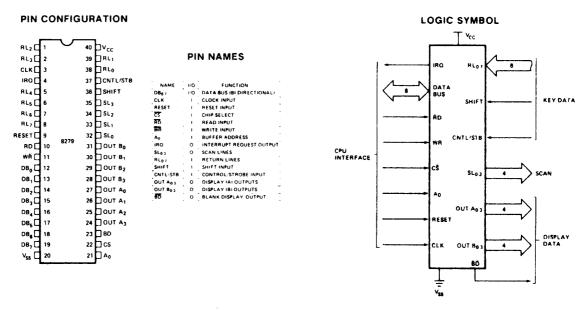

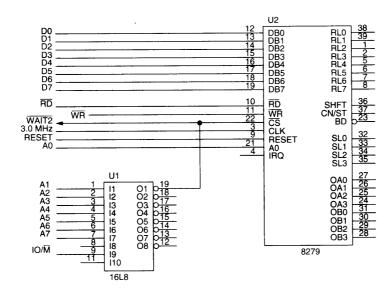

In Figure 10–33, the 8279 is connected to the 8088 microprocessor. The 8279 is decoded to function at 8-bit I/O address 10H and 11H, where port 10H is the data port and 11H is the control port. This circuit uses a PAL16L8 (see Example 10–20) to decode the I/O address for the 8279. Address bus bit A0 selects either the data or control port. Notice that the CS signal selects the 8279 and also provides a signal called WAIT2 that is used to cause two wait states so that this device can function with an 8 MHz 8088.

A ground pin connected to the system ground.

The only signal not connected to the microprocessor is the IRQ output. This is an interrupt request pin and is beyond the scope of this section of the text. Chapter 11 explains interrupts and where they operate and function in a system.

FIGURE 10-33 The 8279 interfaced to the 8088 microprocessor to function at 8-bit I/O ports 10H and 11H.

### **EXAMPLE 10-20**

```

TITLE

Address Decoder

Test 14

PATTERN

REVISION

AUTHOR

Barry B. Brey

COMPANY

BreyCo

7/10/99

DATE

DECODERE PAL16L8

CHIP

1 2 3 4 5 6 7

8

A1 A2 A3 A4 A5 A6 A7 NC IOM GND

;pins 11 12 13 14 15 16 17 18 19 20

NC NC NC NC NC NC NC CS VCC

EOUATIONS

/CS = /A7 * /A6 * /A5 * A4 * /A3 * /A2 * /A1 * IOM

```

### **Keyboard Interface**

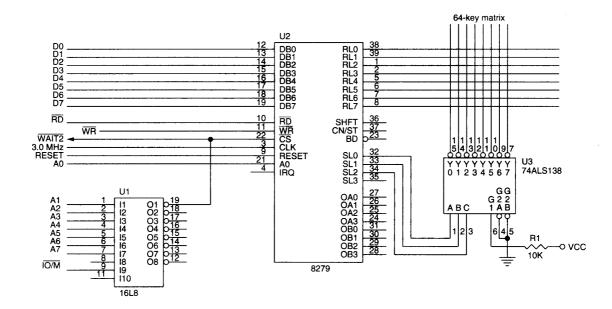

Suppose that a 64-key keyboard (with no numeric displays) is connected through the 8279 to the 8088microprocessor. Figure 10-34 shows this connection, as well as the keyboard. With the 8279, the keyboard matrix is any size from a 2  $\times$  2 matrix (four keys) to an 8  $\times$  8 matrix (64 keys). (Note that each crossover point in the matrix contains a normally open push-button switch that connects one vertical column with one horizontal row when a key is pressed.)

The I/O port number decoded is the same as that decoded for Figure 10-33. The I/O port number is 10H for the data port and 11H for the control port in this circuit.

The 74ALS138 decoder generates eight active low column strobe signals for the keyboard. The selection pins SL2-SL0 sequentially scan each column of the keyboard, and the internal circuitry of the 8279 scans the RL pins, searching for a key switch closure. Pull-up resisters, normally found on input lines of a keyboard, are not required because the 8279 contains its own internal pull-ups on the RL inputs.

FIGURE 10-34 A 64-key keyboard interfaced to the 8088 microprocessor through the 8279.

TABLE 10-4 The 8279 control word summary.

| $D_7$ | $D_6$ | $D_5$ | Function              | Purpose                                                                                 |

|-------|-------|-------|-----------------------|-----------------------------------------------------------------------------------------|

| 0     | 0     | 0     | Mode set              | Selects the number of display positions, left or right entry, and type of keyboard scan |

| 0     | 0     | 1     | Clock                 | Programs the internal clock and sets the scan and de-<br>bounce times                   |

| 0     | 1     | 0     | Read FIFO             | Selects the type of FIFO read and the address of the read                               |

| 0     | 1     | 1     | Read display          | Selects the type of display read and the address of the read                            |

| 1     | 0     | 0     | Write display         | Selects the type of write and the address of the write                                  |

| 1     | 0     | 1     | Display write inhibit | Allows half-bytes to be blanked                                                         |

| 1     | 1     | 0     | Clear                 | Clears the display or FIFO                                                              |

| 1     | 1     | 1     | End interrupt         | Clears the IRQ signal to the microprocessor                                             |

**Programming the Keyboard Interface.** Before any keystroke is detected, the 8279 must be programmed—a more involved procedure than with the 82C55. The 8279 has eight control words to consider before it is programmed. The first three bits of the number sent to the control port (11H, in this example) select one of the eight different control words. Table 10–4 lists all eight control words and briefly describes them.

**Control Word Descriptions.** Following is a list of the control words that program the 8279. Note that the first three bits are the control register number from Table 10–4, which are followed by other binary bits of information as they apply to each control.

### 000DDMMM

Mode set is a command with an opcode of TABLE 10-5 Binary bit assignment 000 and two fields programmed to select the mode of operation for the 8279. The DD field selects the mode of operation for the displays (see Table 10-5), and the MMM field selects the mode of operation for the keyboard (see Table 10-6).

The DD field selects either an 8- or 16-digit display, and determines whether new data are entered to the rightmost or leftmost display position. The MMM field is quite a bit more complex: it provides encoded, decoded, or strobed keyboard operation.

In encoded mode, the SL outputs are activehigh, and follow the binary bit pattern 0 through 7 or 0 through 15, depending whether 8- or 16-digit displays are selected. In decoded mode, the SL outputs are active-low, and only one of the four outputs is low at any given instant. The decoded outputs repeat the pattern: 1110, 1101, 1011, and 0111. In strobed mode, an active-high pulse on the CN/ST input pin strobes data from the RL pins into an internal FIFO, where they are held for the microprocessor.

It is also possible to select either 2-key lockout or N-key rollover. 2-key lockout prevents two keys from being recognized, if pressed simultaneously. N-key rollover will accept all keys pressed simultaneously, from first to last.

for DD of the mode set control word.

| DD | Function                          |

|----|-----------------------------------|

| 00 | 8-digit display with left entry   |

| 01 | 16-digit display with left entry  |

| 10 | 8-digit display with right entry  |

| 11 | 16-digit display with right entry |

TABLE 10-6 Binary bit assignment for MMM of the mode set control word.

| ммм | Function                               |  |  |  |  |

|-----|----------------------------------------|--|--|--|--|

| 000 | Encoded keyboard with 2-key lockout    |  |  |  |  |

| 001 | Decoded keyboard with 2-key lockout    |  |  |  |  |

| 010 | Encoded keyboard with N-key rollover   |  |  |  |  |

| 011 | Decoded keyboard with N-key rollover   |  |  |  |  |

| 100 | Encoded sensor matrix                  |  |  |  |  |

| 101 | Decoded sensor matrix                  |  |  |  |  |

| 110 | Strobed keyboard, encoded display scan |  |  |  |  |

| 111 | Strobed keyboard, decoded display scan |  |  |  |  |

### 001PPPPP

The clock command word programs the internal clock divider. The code PPPPP is a prescaler that divides the clock input pin (CLK) to achieve the desired operating frequency of approximately 100 KHz. An input clock of 1 MHz thus requires a prescaler of 01010, for PPPPP.

### 010Z0AAA

The read FIFO control word selects the address of a keystroke from the internal FIFO buffer. Bit positions AAA select the desired FIFO location from 000 to 111, and Z selects auto-increment for the address. Under normal operation, this control word is used only with the sensor matrix operation of the 8279.

### 011ZAAAA

The display read control word selects the read address of one of the display RAM positions for reading through the data port. AAAA is the address of the position to be read and Z selects auto-increment mode. This command is used if the information stored in the display RAM must be read.

### 100ZAAAA

The write display control word selects the write address of one of the displays. AAAA addresses the position to be written to through the data port, and Z selects autoincrement so subsequent writes through the data port are to subsequent display positions.

### **1010WWBB**

The display write inhibit control word inhibits writing to either half of each display RAM location. The leftmost W inhibits writing to the leftmost four bits of the display RAM location, and the rightmost W inhibits the rightmost four bits. The BB field functions in a like manner, except that they blank (turn off) either half of the output pins.

### 1100CCFA

The clear control word clears the display, the FIFO, or both the display and FIFO. Bit F clears the FIFO and the display RAM status, and sets the address pointer to 000. If the CC bits are 00 or 01, all of the display RAM locations become 0000000; if CC = 10, all locations become 00100000; and if CC = 11, all locations become 111111111.

111E000

The **end of interrupt** control word is issued to clear the IRQ pin to zero in the sensor matrix mode. If E is a 1, the special error mode is used. In the special error mode, the status register indicates if multiple key closures have occurred.

The large number of control words make programming the keyboard interface appear complex. Before anything is programmed, the clock divider rate must be determined. In the circuit illustrated in Figure 10–34, we use a 3.0 MHz clock input signal. To program the prescaler to generate a 100 KHz internal rate, we program PPPPP of the clock control word with a 30 or 11110<sub>2</sub>.

The next step involves programming the keyboard type. The example keyboard in Figure 10–34 is an encoded keyboard. Notice that the circuit includes an external decoder that converts the encoded data from the SL pins into decoded column-selection signals. We are free in this example to choose either 2-key lockout or N-key rollover, but most applications use 2-key lockout.

Finally, we program the operation of the FIFO. Once the FIFO is programmed, it never needs to be reprogrammed unless we need to read prior keyboard codes. Each time a key is typed, the data are stored in the FIFO; if they are read from the FIFO before the FIFO is full (eight characters), the data from the FIFO follows the same order as the typed data. Example 10–21 provides the software required to initialize the 8279 to control the keyboard illustrated in Figure 10–34.

### **EXAMPLE 10-21**

```

;Initialization dialog for the keyboard interface

;of Figure 10-34.

0000

B0 3E

MOV

AL,00111110B

;program clock

0002

E6 11

OUT

11H, AL

0004

B0 00

MOV

AL,0

0006

E6 11

OUT

11H,AL

;program mode

0008 B0 50

MOV

AL,01010000B

000A E6 11

OUT

11H,AL

;program FIFO

```

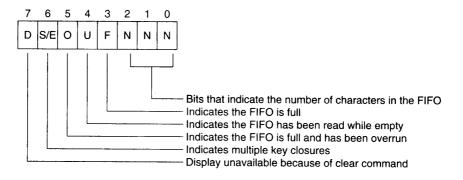

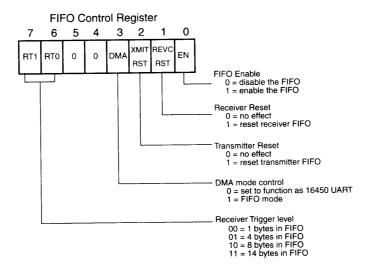

Once the 8279 is initialized, a procedure is required to read data from the keyboard. We determine whether a character is typed in the keyboard by looking at the FIFO status register. Whenever the control port is addressed by the IN instruction, the contents of the FIFO status word is copied into the AL register. Figure 10–35 shows the contents of the FIFO status register and defines the purpose of each status bit.

FIGURE 10-35 The 8279-5 FIFO status register.

FIGURE 10-36 The (a) scanned keyboard code and (b) strobed keyboard code for the 8279-5 FIFO.

The procedure listed in Example 10-22 first tests the FIFO status register to see whether it contains any data. If NNN = 000, the FIFO is empty. Upon determining that the FIFO is not empty, the procedure inputs data to AL and returns with the keyboard code in AL.

#### **EXAMPLE 10-22**

```

;A procedure that reads data from the FIFO and

;returns it in AL.

MASKS EOU

= 0007

0000

READ

PROC

NEAR

AL, 11H

;read status

0000

IN

E4 11

;test NNN

TEST

AL. MASKS

0002

A8 07

; if NNN = 0

0004

74 FA

.17.

READ

IN

AL,10H

;read FIFO data

0006

E4 10

RET

0008

C3

ENDP

READ

0009

```

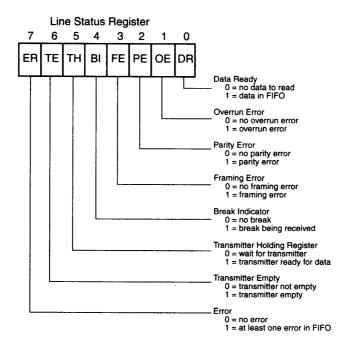

The data found in AL upon returning from the subroutine contains raw data from the keyboard. Figure 10-36 shows the format of this data for both the scanned and strobed modes of operation. The scanned code is returned from our keyboard interface and is converted to ASCII code by using the XLAT instruction with an ASCII code lookup table. The scanned code is returned with the row and column number occupying the rightmost six bits.

The SH bit shows the state of the shift pin and the CT bit shows the state of the control pin. In the strobed mode, the contents of the eight RL inputs appear as they are sampled by placing a logic 1 on the strobe input pin to the 8279.

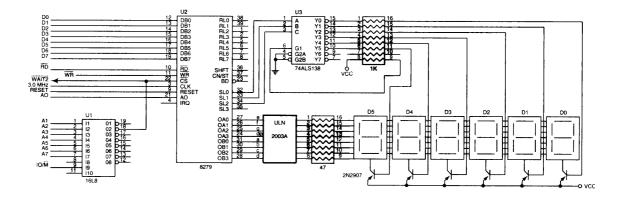

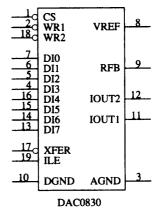

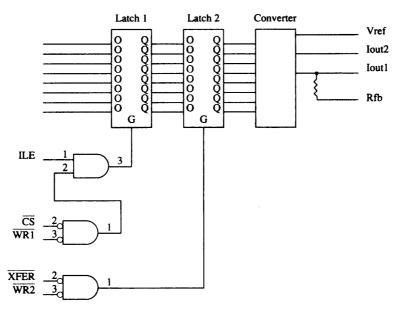

# Six-Digit Display Interface

Figure 10-37 depicts the 8279 connected to the 8088 microprocessor and a 6-digit numeric display. This interface uses a PAL16L8 (program not shown) to decode the 8279 at I/O ports 20H (data) and 21H (control/status). The segment data are supplied to the displays through the OUTA and OUTB pins of the 8279. These bits are buffered by a segment driver (ULN2003A) to drive the segment inputs to the display.

A 74ALS138 3-to-8 line decoder enables the anode switches of each display position. The SL2-SL0 pins supply the decoder with the encoded display position from the 8279. Notice that the left-hand display is at position 0101 and the right-hand display is at position 0000. These are the addresses of the display positions, as indicated in control words for the 8279.

It is necessary to choose resistor values that allow 60 mA of current flow per segment. In this circuit, we use 47 ★ resistors. If we allow 60 mA of segment current, then the average segment current is 10 mA, or onesixth of 60 mA because current only flows for one-sixth of the time through a segment. The anode switches must supply the current for all seven segments plus the decimal point. Here, the total anode current is  $8 \times 60$ mA, or 480 mA.

FIGURE 10-37 A 6-digit numeric display interfaced to the 8279.

Example 10–23 lists the initialization dialog for programming the 8279 to function with this 6-digit display. This software programs the display and clears the display RAM.

### **EXAMPLE 10-23**

```

; Initialization dialog for the 6-digit display of

;Figure 10-37.

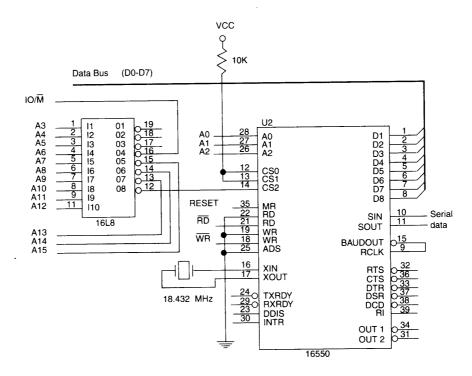

0000